#### 1 まえがき

近年、携帯電話に代表されるデジタル電子機器は高機能化に伴い、IC の集積化、信号周波数の高速化が進んでいます。IC の高集積化、高周波化は電源電流の増加を招くため、電圧変動による誤動作、受信感度の低減、そして放射ノイズの増大といった問題を引き起します。これらの問題を解決するために、従来から様々な検討が行われてきました。積層コンデンサを電源ピンに近づけて配置するといったものがこれに当たります。しかしながら、これらは各電源ピンにコンデンサを実装するため、使用するコンデンサの数量が多くなるという弊害が生じることになります。そこで、今回は実装位置の工夫と高性能コンデンサを使用することによって使用数量の削減とノイズ低減の両方を達成することに成功したので、以下にその詳細を示します。

#### 2 コンデンサの特件について

3 端子構造の EMI 除去フィルタや 2 端子積層セラミックコンデンサの特性は弊社 web ページ "http://www.murata.co.jp/emc/knowhow/pdfs/17to19.pdf#page=2"を参照してください。

## 3 OMAP5912 電源ライン評価基板

効率的なコンデンサの実装方法を検討するために、日本 Texas Instruments(株)様、ロステーカ (株)様と共同で携帯電話用 DSPOMAP5912 電源ラインの評価基板を作成しました。まず評価基板の概要を説明します。

#### 3.1 OMAP5912 について

OMAP5912 は音声や画像のデジタル処理を行うTMS320C55x™DSPコアとOS等の処理を行う、ARM926EJ-Sプロセッサを組み合わせたTexas Instruments(株)様製プロセッサです。デジタル家電 全 般 に 使 う こ と が で き 、主 に 携 帯 電 話 に 使 わ れ て い ま す 。詳 し く は"http://www.tij.co.jp/jsc/docs/dsps/product/omap/omap5912.htm"を参照してください。

## 3.2 OMAP5912 の電源ラインについて

OMAP5912 は以下の 6 つの電源ラインが必要となります。

表 1 OMAP5912 の電源ライン

|           | 電圧[V]                   | 概要                            |

|-----------|-------------------------|-------------------------------|

| VDD_RTC   | 1.525 <sup>~</sup> 1.65 | Real Time Clock(内部時計)の電源      |

| VDD_CORE  | 1.525~1.65              | ARM926EJ-S の電源                |

| VDD_DLL   | 1.525~1.65              | Delayed Lock Loop(PLL の一種)の電源 |

| VDD_SDRAM | 1.65 <sup>~</sup> 1.95  | DDR-SDRAM とのやりとりのための電源        |

| VDD_DSP   | 1.525~1.65              | TMS320C55x™DSP の電源            |

| VDD_3V3   | 3~3.6                   | 他のデバイスとのやりとりのための電源            |

VDD RTC と VDD DLL は消費電力が他の電源ラインより低いため評価からはずしました。

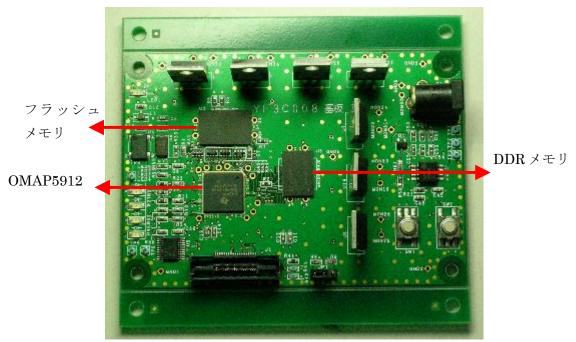

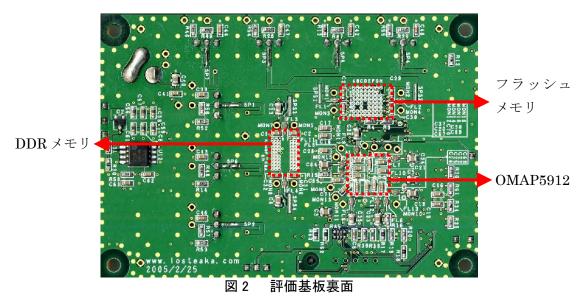

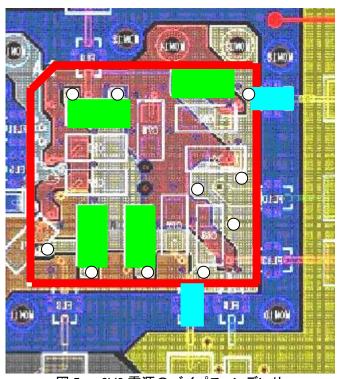

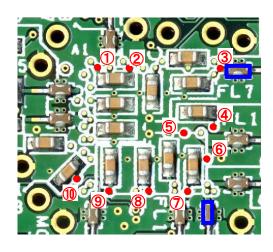

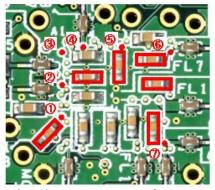

#### 3.3 評価基板の外観

外観を図 1,2 に示します。OMAP5912、フラッシュメモリ、DDR メモリのみという最小構成をとっています。OMAP5912 が常に動作するように日本 Texas Instruments(株)様にプログラムしていただき、最もノイズの高い状態での評価を可能としています。

図 1 評価基板表面

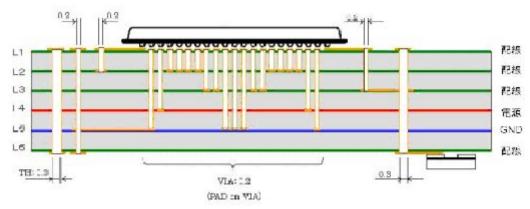

## 3.4 評価基板の層構成

層構成を図3に示します。評価基板はIVHの6層基板で、電源層はL4層、GND層はL5層、部品の実装はICと反対側のL6層となっています(IVHはInterstitial Via Holeの略で層間をつなぐ穴を意味します。IVH基板はスルーホールを途中で止めたり、中間層だけにスルーホールを作ることができることを特徴とした多層基板です)。

図3 評価基板の層構成

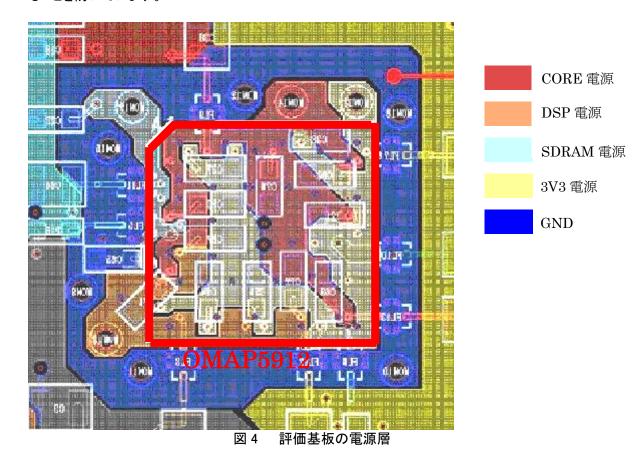

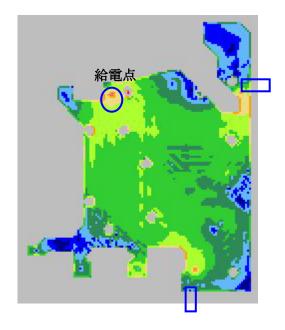

#### 3.5 電源パターンの構成

電源層の構成(L4層)を図4に示します。IC 直下の電源層を島のように分離し、外側の電源パターンとは3端子構造のEMI除去フィルタを使って接続しています。このように配置することで、ICから発生するノイズ電流は島状の電源パターンの外にでるためにはフィルタを必ず経由しなければならなくなるため、高いデカップリング効果を得ることができます(詳しくは補足資料:電源電圧の安定化、ノイズ電流の流出防止の基本的な考えを参照してください)。また、IC直下の島状の電源層と外の電源層をGNDにより隔離することで、ノイズ電流がカップリングにより直接外に流出することを防いでいます。

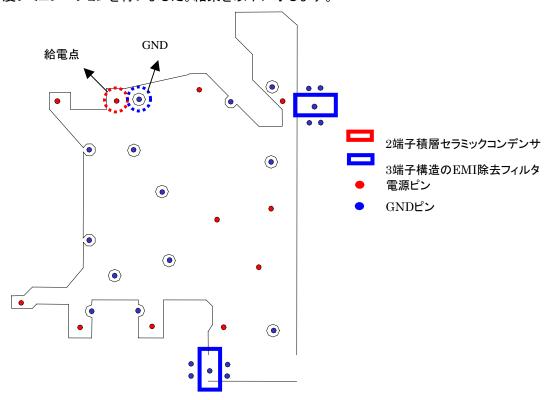

## 3.6 バイパスコンデンサの構成

3V3 電源のバイパスコンデンサの配置を図 5 に示します。他の電源用コンデンサの配置等も考慮し、3 端子構造の EMI 除去フィルタを 2 個、2 端子積層セラミックコンデンサを 4 個実装可能としています。

使用した部品を以下に示します。

- 3 端子構造の EMI 除去フィルタ: NFM18PS474R0J3 0.47 μ F

- 2 端子積層セラミックコンデンサ: 積層型セラミックコンデンサ 0.01 μ F

2 端子積層セラミック コンデンサ 3 端子構造の

EMI 除去フィルタ

○ 電源ピン

図 5 3V3 電源のバイパスコンデンサ

## 4 OMAP5912 電源ライン評価基板の評価結果

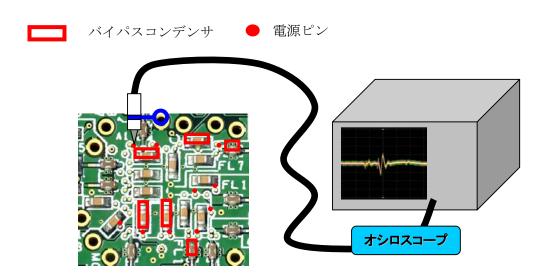

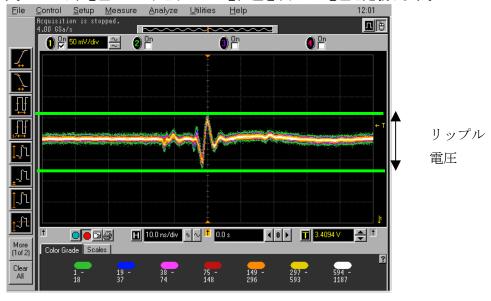

#### 4.1 リップル電圧の評価方法

IC の各電源ピンと最寄りの GND 間の電位差をオシロスコープにより測定しました。オシロスコープは Agilent 製 54846A、プローブは Agilent 製 1161A を使用しました。

図 6 リップル電圧の測定方法

測定結果の例を図7に示します。電源電圧は本来一定の電圧となるはずですが、図7のように変動してしまいます。ここでは、電圧のピークとボトムの電位差をリップル電圧と定義します。

図7 リップル測定例

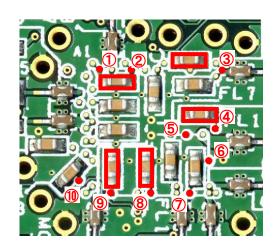

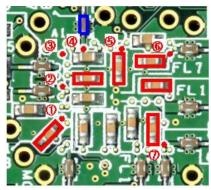

## 4.2 リップル電圧の評価結果

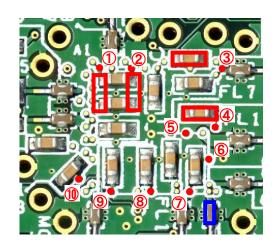

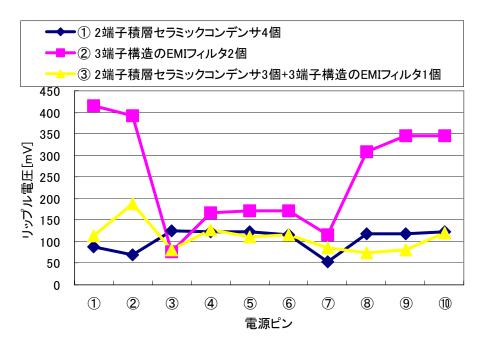

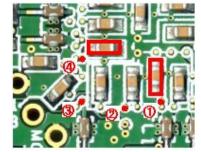

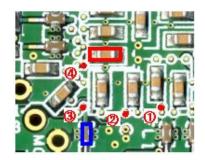

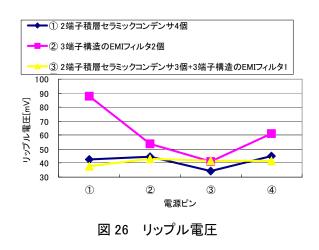

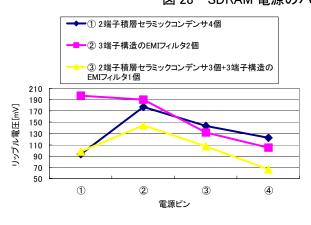

バイパスコンデンサを①2 端子積層セラミックコンデンサのみ使用した場合、②3 端子構造の EMI 除去フィルタのみ使用した場合、③2 端子積層セラミックコンデンサと 3 端子構造の EMI 除去フィ ルタを組み合わせて使用した場合の 3 通り評価しました。3V3 電源の評価結果を示します。他の 電源の評価結果は補足資料参照してください。

2 端子積層

3 端子構造の EMI

セラミックコンデンサ

除去フィルタ

電源ピン

①~⑩ 評価対象となる電源ピンの番号

図8 2端子積層セラミックコンデンサのみをバイパスコンデンサとした場合の配置

3端子構造の EMI 除去フィルタのみをバイパスコンデンサとした場合の配置 図 9

図 10 2 端子積層セラミックコンデンサと3 端子構造の EMI 除去フィルタを組み合わせた場合の配置

図 11 リップル電圧の評価結果

- ・2 端子積層セラミックコンデンサのみを使用した場合のほうが 3 端子構造の EMI 除去フィルタの みを使用したよりもリップル電圧が低い。

- ・特にリップル電圧が高い②、③番の電源ピンを対策することでリップル電圧を平均的に抑えることができる。

3 端子構造の EMI 除去フィルタよりも ESL が高い 2 端子積層セラミックコンデンサで対策した場合の方がリップル電圧を良く抑えられた原因は、2 端子積層セラミックコンデンサは電源ピンの間近に実装できるため、電源パターンのインピーダンスが小さかったためであると考えられます。 3V3 電源のパターンは図 4 で示される通り複雑になっており、電源ピンから 3 端子構造の EMI 除去フィルタまでのパターンのインピーダンスはかなり高くなっていることが考えられます。

この件については次にシミュレーションを使って考察します。

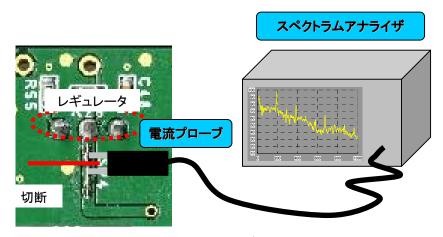

#### 4.3 電源ラインに流れるノイズ電流の評価方法

各電源ラインのレギュレータ直後に電流プローブを直列に実装し、IC 直下の電源パターンから電源側に漏れ出たノイズ電流をスペクトラムアナライザにより測定しました。スペクトラムアナライザは Agilent 製 E4404B、電流プローブは Tektronix 製 CT6 を使用しました。

図 12 電源ラインノイズ測定方法

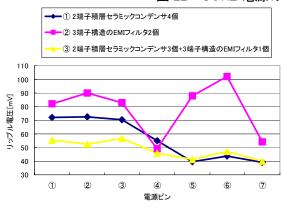

#### 4.4 電源ラインに流れるノイズ電流の評価結果

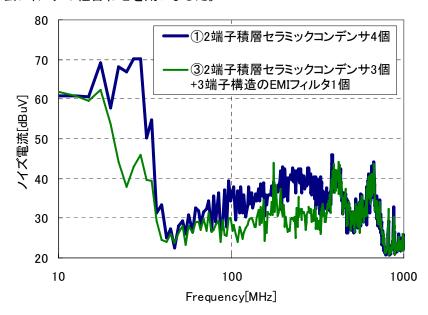

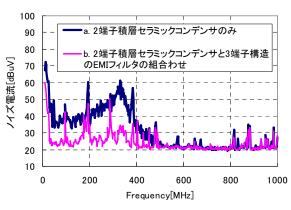

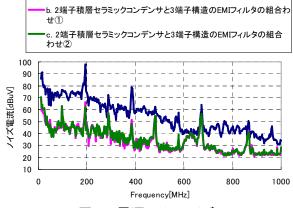

3V3 電源でのノイズ電流の評価結果を示します。バイパスコンデンサの構成は 4.2 リップル電圧の評価での①2 端子積層セラミックコンデンサのみの③2 端子積層セラミックコンデンサと 3 端子構造の EMI 除去フィルタの組合わせを用いました。

図 13 3V3 の電源ラインノイズ

3 端子構造の EMI 除去フィルタを使用した構成のほうが高いノイズ除去効果があることがわかります。これは、3 端子構造の EMI 除去フィルタは 2 端子積層セラミックコンデンサよりも ESL が低いためであると考えられます(詳しくは補足資料:電源電圧の安定化、ノイズ電流の流出防止の基本的な考え方を参照してください)

## 5 シミュレーションによる考察

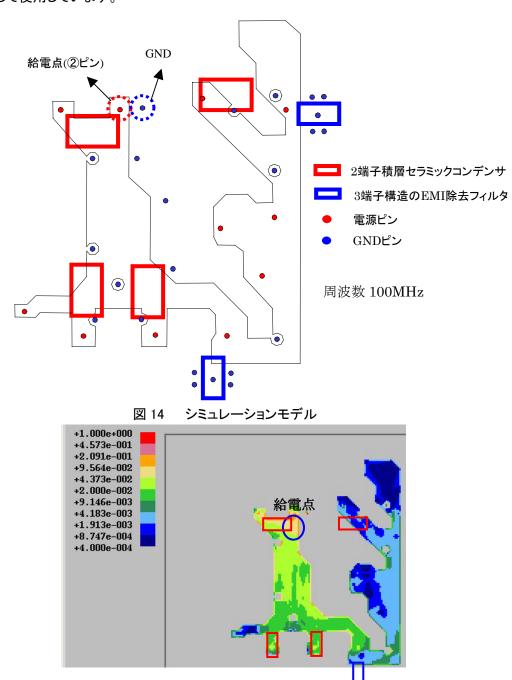

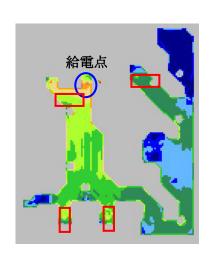

4.3 でバイパスコンデンサに 3 端子構造の EMI 除去フィルタのみを使用した場合にリップル電圧が高かったのは電源パターンのインピーダンスが高いためであると考察しました。このことを確認するために、アプライドシミュレーション製シミュレータ Apsim Rpath を使用し電源ピンと GND ピン間のインピーダンスを計算します。シミュレーションモデルを図 14 に示します。最もリップル電圧の高かった 3V3 電源の②番ピンを対象とし、バイパスコンデンサの構成を変更した場合のリップル電圧の実測値と電源ピン-GND ピン間のインピーダンスを比較しました。結果を以下に示します。 2 端子積層セラミックコンデンサ及び、3 端子構造の EMI 除去フィルタは実測値より等価回路モデルを作成して使用しています。

図 15 2 端子積層セラミックコンデンサ+3 端子構造の EMI 除去フィルタ

図 16 2 端子積層セラミ ックコンデンサのみ

図 17 3 端子構造の EMI 除去フィルタのみ

| 表 2  | 宝測レシミュレ  | ノーションの比較 |

|------|----------|----------|

| 1X Z | 一大川にフミエレ | ノーノコンひルギ |

| 衣と            |              |                |  |  |

|---------------|--------------|----------------|--|--|

|               | リップル実測値[mV]  | 電源ピン-GND 間インピー |  |  |

|               |              | ダンス[Ω]         |  |  |

| 2 端子積層セラミック   | 180.5(1)     | 0.365(1)       |  |  |

| コンデンサ+        |              |                |  |  |

| 3 端子構造の EMI 除 |              |                |  |  |

| 去フィルタ         |              |                |  |  |

| 2 端子積層セラミック   | 187.7(1.04)  | 0.386(1.06)    |  |  |

| コンデンサのみ       |              |                |  |  |

| 3 端子構造の EMI 除 | 391.2 (2.17) | 0.805(2.20)    |  |  |

| 去フィルタのみ       |              |                |  |  |

- \* 100MHz での 2 端子積層セラミックコンデンサのインピーダンスは 0.179Ω 3 端子構造の EMI 除去フィルタのインピーダンスは 0.005Ω

- \*()内は2端子積層セラミックコンデンサ+3端子構造のEMI除去フィルタの値を1としたときの相対置

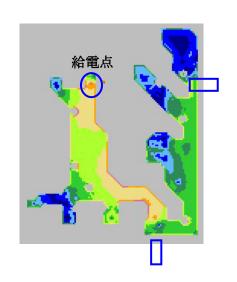

- ・3 端子構造の EMI 除去フィルタのみの場合の電源ピン-GND 間インピーダンスは 2 端子積層セラミックコンデンサがある場合と比較して 2 倍以上高くなっており、リップルの実測値と傾向が一致しています。

- ・3 端子構造の EMI 除去フィルタのみの場合の電源ピン-GND 間インピーダンスは 3 端子構造の EMI 除去フィルタのインピーダンスよりも 2 桁高く、ほぼパターンのインピーダンスが支配的であると考えられます。

## シミュレーションモデルの改良

図 14 でからわかるように、3V3 電源のパターン形状がいびつであるため、電源パターンのインピーダンスが高くなっていることが考えられます。そこで図 18 に示すように、電源パターン形状を改良し再度シミュレーションを行いました。結果を以下に示します。

図 18 パターン形状の改良

図 19 改良モデル解析結果

表 3 改良前と改良後の電源ピン-GND 間インピーダンス

|                      | 電源ピン-GND 間インピーダンス[Ω] |        |  |

|----------------------|----------------------|--------|--|

|                      | 改良前                  | 改良後    |  |

| 3 端子構造の EMI 除去フィルタのみ | 0.805                | 0.3086 |  |

電源パターンを改良することでインピーダンスが半分以下になりました。これは、改良前は上側の3端子構造のEMI除去フィルタがほとんど使われなかった(図17)のに対して、改良後は2つの3端子構造のEMI除去フィルタを使って電流が流れるため、インピーダンスが半減したものと考えられます。また、電源パターンがベタパターンに近くなったためパターンのインピーダンスが低くなっていることもインピーダンスの低減につながっていると考えられます。

#### 6 まとめ

#### 電源電圧の安定化について

- ・リップル電圧を十分抑えるためには、電源ピンの周辺に複数のバイパスコンデンサを使用する 必要があります。

- ・電源ピンからバイパスコンデンサまでの距離が長い場合、リップル電圧は電源パターンのインピーダンスが支配的であるため、パターンのインピーダンスを低くすることでバイパスコンデンサの数を減らすことができると考えられます。

## 電源ラインノイズ電流について

電源パターンを GND で隔離することで島状にし、3 端子構造の EMI 除去フィルタを使用することで ノイズ電流の流出を十分抑えることができます。

# 補足資料① 電源電圧の安定化、ノイズ電流の流出防止の基本的な考え方

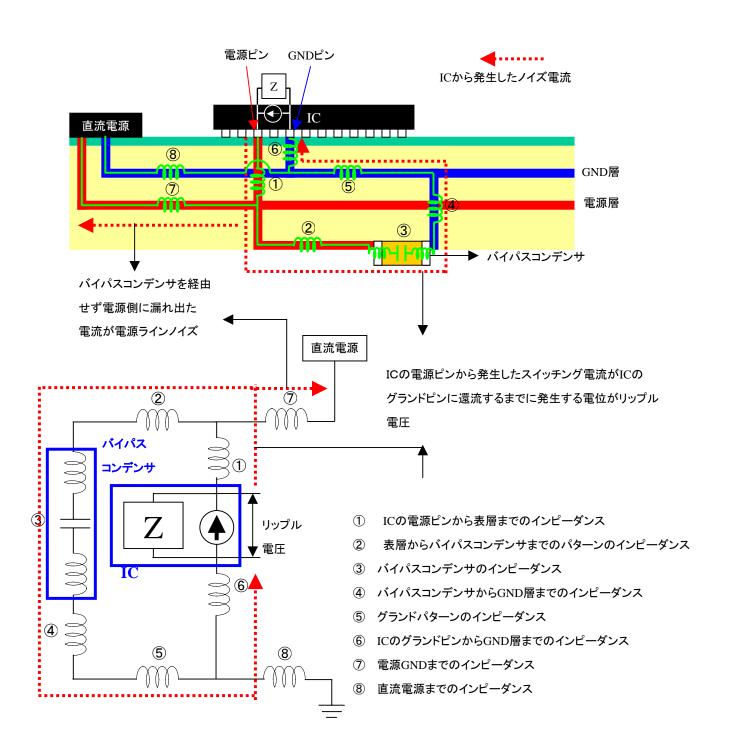

リップル電圧と電源ラインノイズの発生原理を図20に示します。

IC が動作するとき、IC のスイッチングによって IC の負荷容量に電荷が充放電されることによって、ノイズ電流が電源ピンから発生します。この電流はコンデンサを介して GND ピンに戻ります。このとき、IC は等価的に電流源と考えることができ、IC の電源ピンから発生するノイズ電流がGNDピンに戻ってくるまでに発生した電圧が電源電圧の変動(リップル電圧)として現れます。また、コンデンサを介して GND ピンに戻らずに、電源側に流れた電流が電源ラインノイズとなります。

#### 電源電圧を安定化する方法

リップル電圧を下げるためには図 20 の①~⑥のインピーダンスを全て低くする必要があります。 したがって、電源電圧を安定化するためには以下の方法が考えられます。

- ・バイパスコンデンサを電源ピンにできるだけ近づけて実装する(②、⑤を小さくする)。

- ・バイパスコンデンサの ESL をできるだけ小さくする(③を小さくする)。

- ・電源パターン及び、GND パターンのインピーダンスをできるだけ小さくする(②、⑤を小さくする)。

- ・スルーホールの長さを短く、太く、複数並列にすることでインピーダンスを下げる(①,④,⑥を小さくする)。

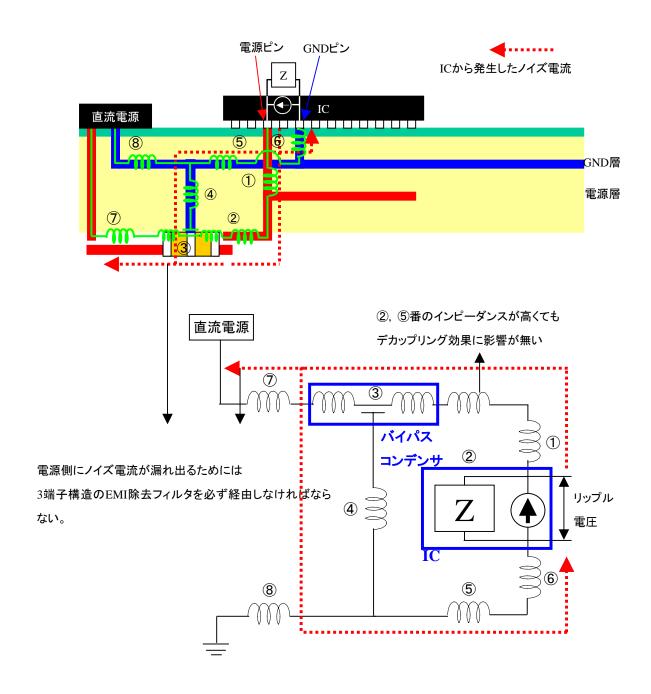

#### ノイズ電流の流出を防止する方法

ノイズ電流の流出を防止するためには、②~⑤のインピーダンスを低くする必要があります。しかし、図 21 に示すように、3 端子構造の EMI 除去フィルタを用い、直流電源側にノイズ電流が漏れ出るためにはバイパスコンデンサを必ず経由するように実装することで、②、⑤をデカップリングに無関係にすることができます。したがって、ノイズ電流の流出を防止するためには以下の方法が考えられます。

- ・3 端子構造の EMI 除去フィルタを用い、直流電源側にノイズ電流が漏れ出るためには必ずバイパスコンデンサを経由するようにする(②、⑤番をデカップリングに無関係にする)。

- ・バイパスコンデンサ(デカップリングコンデンサ)の ESL をできるだけ小さくする(③を小さくする)。

- ・GND パターンのインピーダンスをできるだけ小さくする(®を小さくする)。

- ・3 端子構造の EMI 除去フィルタとグランド間のスルーホールの長さを短く、太く、複数並列にすることでインピーダンスを下げる(④を小さくする。)

図 20 リップル電圧、電源ラインノイズの発生原理

図 21 3 端子構造の EMI 除去フィルタの実装例

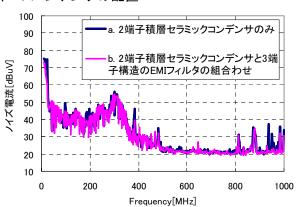

補足資料②:他の電源ラインにおけるリップル電圧と 電源ラインノイズの評価結果

#### · CORE 電源

2 端子積層セラミック

3 端子構造の EMI

電源ピン

コンデンサ

除去フィルタ

①~⑦ 評価対象となる電源ピンの番号

a.2 端子積層セラミックコンデンサのみの 組合わせ

b. 2 端子積層セラミックコンデンサと 3 端子構造の EMI 除去フィルタの組合わせ

図 22 CORE 電源のバイパスコンデンサの配置

図 23 リップル電圧

図 24 電源ラインノイズ

### • DSP 電源

a.2 端子積層セラミックコンデンサのみの 組合わせ

b. 2 端子積層セラミックコンデンサと 3 端子構造の EMI 除去フィルタの組合わせ

図 25 DSP 電源のバイパスコンデンサの配置

図 27 電源ラインノイズ

#### ·SDRAM 電源

a.2 端子積層セラミックコンデンサ のみの汲み合わせ

b.2 端子積層セラミックコンデンサ と3 端子構造の EMI 除去フィルタ の組合わせ①

c. 2 端子積層セラミックコンデン サと3 端子構造の EMI 除去フィ ルタの組合わせ②

図 28 SDRAM 電源のバイパスコンデンサの配置

図 29 リップル電圧

**-**a. 2端子積層セラミックコンデンサのみ

図 30 電源ラインノイズ

#### お願い

1. 当カタログに記載の製品について、その故障や誤動作が人命または財産に危害を及ぼす恐れがある等の理由により、高信頼性が要求される以下の用途でのご使用をご検討の場合、または、当カタログに記載された用途以外でのご使用をご検討の場合は、必ず事前に当社営業本部または最寄りの営業所までご連絡ください。

航空機器 宇宙機器 海底機器 発電所制御機器 医療機器 輸送機器(自動車、列車、船舶等) 交通用信号機器 防災/防犯機器 情報処理機器 その他上記機器と同等の機器

2. 当カタログの記載内容は 2006 年 1 月現在のものです。

記載内容について、改良のため予告な〈変更することや供給を停止することがございますので、ご注文に際してはご確認〈ださい。

記載内容にご不明の点がございましたら当社営業本部または最寄りの営業所までお問い合せください。

- 3. 製品によっては、守らないと発煙、発火等に至る可能性のある定格やΔ注意(保管・使用環境、 定格上の注意、実装上の注意、取扱上の注意)を記載しておりますので、必ずご覧下さい。

- 4. 当カタログには、紙面の都合上代表的な仕様しか記載しておりませんので、ご注文にあたっては詳細な仕様が記載されている納入仕様書の内容をご確認いただくか承認図の取交しをお願いします。

- 5. 当カタログに記載の製品の使用もしくは当カタログに記載の情報の使用に際して、当社もしく は第三者の知的財産権その他の権利にかかわる問題が発生した場合は、当社はその責を負 うものではありません。また、これらの権利の実施権の許諾を行うものではありません。

- 6. 当カタログに記載の製品のうち、「外国為替及び外国貿易法」に定める規制貨物等に該当する ものについては、輸出する場合、同法に基づ〈輸出許可が必要です。

- 7. 当社の製造工程では、モントリオール議定書で規制されているオゾン層破壊物質(ODS)は一切使用しておりません。