86mm 1U Front End AC-DC Power Supply

NB: D1U86P-W-1600-12-HB3DC Model Shown

#### **PRODUCT OVERVIEW**

The D1U86P-W-1600-12-HBxDC products are high efficiency 1600 watt, power factor corrected front end supplies with a 12V main output and a 12V (30W) standby. They have current sharing and up to 8 supplies may be operated in parallel. The supplies may be hot plugged, they recover from over-temperature faults, and have logic and PMBus™ monitoring and control. Their low profile 1U package and >38.6W/cubic inch power density make them ideal for delivering reliable, efficient power to servers, workstations, storage systems and other 12V distributed power systems.

| ORDERING GUIDE         |           |            |            |         |        |               |        |

|------------------------|-----------|------------|------------|---------|--------|---------------|--------|

| Part Number            | Powe      | Main       | Standby    | Airflow | Handle |               |        |

| Fait Nullibei          | (90-264V) | (108-264V) | (180-264V) | Output  | Output | AIIIIOW       | Colour |

| D1U86P-W-1600-12-HB4DC | 1200W     | 00W 1350W  | 1600W      | 12V     | 12V    | Back to Front | Red    |

| D1U86P-W-1600-12-HB3DC |           |            |            |         |        | Front to      | Blue   |

| INPUT CHARACTERISTICS             |                              |      |         |      |       |

|-----------------------------------|------------------------------|------|---------|------|-------|

| Parameter                         | Conditions                   | Min. | Nom.    | Max. | Units |

| Input Voltage Operating Range     |                              | 90   | 115/230 | 264  | Vac   |

| Frequency                         |                              | 47   | 50/60   | 63   | Hz    |

| Turn-on Voltage                   | Ramp up                      | 81   |         | 89   | Vac   |

| Turn-off Voltage                  | Ramp down                    | 70.5 | 73      | 78   | Val   |

| Maximum Input Current             | 1200W, 100Vac                |      |         | 14.1 | Arms  |

| Inrush Current                    | At 264Vac at 25°C cold start |      |         | 35   | Apk   |

| Power Factor                      | At 230Vac, half load         |      | 0.98    |      |       |

| F#:-i (000)/)ldi f                | 20% load                     | 90   |         |      |       |

| Efficiency (230Vac) excluding fan | 50% load                     | 94   |         |      | %     |

| load                              | 100% load                    | 91   |         |      |       |

| OUTPUT VOLTA      | GE CHARACTERISTICS                    |                 |       |      |        |        |

|-------------------|---------------------------------------|-----------------|-------|------|--------|--------|

| Output<br>Voltage | Parameter                             | Conditions      | Min.  | Тур. | Max.   | Units  |

|                   | Voltage Set Point                     | 50% load        | 12.17 | 12.2 | 12.23  | Vdc    |

|                   | Line and Load Regulation              |                 | 11.4  |      | 12.6   | vuc    |

|                   | Droop                                 |                 |       | 3.10 |        | mV/A   |

| 12V               | Ripple Voltage & Noise <sup>1</sup>   | 20MHz Bandwidth |       |      | 120    | mV p-p |

| IZV               | Output Current (230 Vac) <sup>2</sup> |                 | 0     |      | 133.4  | Α      |

|                   | Output Current (120 Vac) <sup>2</sup> |                 | 0     |      | 112.5  | Α      |

|                   | Output Current (100 Vac) <sup>2</sup> |                 | 0     |      | 100.0  | Α      |

|                   | Load Capacitance                      |                 |       |      | 10,000 | μF     |

|                   | Voltage Set Point                     | 50% load        | 11.97 | 12.0 | 12.02  | Vdc    |

| 12VSB             | Ripple Voltage & Noise <sup>1</sup>   | 20MHz Bandwidth |       |      | 120    | mV p-p |

|                   | Output Current                        |                 | 0     |      | 2.5    | Α      |

<sup>1</sup>Ripple and noise measured with a parallel combination of a 1.0μF ceramic and 10μF tantalum capacitor on each of the power module outputs. A short coaxial cable connected directly to the input of a scope is required.

#### **FEATURES**

| ■ 1600W  | output | power  |

|----------|--------|--------|

| - 100011 | output | POVVOI |

- 94% minimum efficiency at 50% load

- 12V main output

- 12V standby output of 30W

- 1U height: 3.4" x 7.78" x 1.59"

- 38.6 Watts per cubic inch density

- N+1 redundancy, including hot plugging (up to 8 in parallel)

- Droop Current sharing both outputs

- Overvoltage, overcurrent, overtemperature protection

- Internal cooling fan (variable speed)

- PMBus<sup>TM</sup> / I<sup>2</sup>C interface monitoring and control

- RoHS compliant

- Two Year Warranty

Certificate and Test Report

<sup>&</sup>lt;sup>2</sup>To meet ripple and transient step load specifications a minimum load of 4A is required.

| OUTPUT CHARACTERISTICS                                      |                                   |      |      |      |       |

|-------------------------------------------------------------|-----------------------------------|------|------|------|-------|

| Parameter                                                   | Conditions                        | Min. | Тур. | Max. | Units |

| Output Rise Monotonicity                                    | No voltage excursion              |      |      |      |       |

| Startup Time                                                | AC ramp up                        |      | 1.5  | 3    | S     |

| Transient Response                                          | 12V, 50% load step, 1.0Aµs di/dt  |      | 600  |      | mV    |

| Transient Response                                          | 12VSB, 50% load step,1.0Aµs di/dt |      | 600  |      | IIIV  |

| Current sharing accuracy (up to 8 in parallel) <sup>3</sup> | At 100% load                      |      |      | ±5   | %     |

| Hot Swap Transients                                         | All outputs remain in regulation  |      |      | 5    | %     |

| Holdup Time                                                 | At full load                      | 12   |      |      | ms    |

<sup>3</sup> Load current of 100% applies to each power module max load connected in an N+1 configuration; therefore the total load will be "N" x 100%. The share accuracy of ±5% is a fixed percentage irrespective of total loading and number of units connected in parallel.

| ENVIRONMENTAL CHARACTERISTICS       |                                                                            |                                                                                                            |      |           |         |  |  |

|-------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|-----------|---------|--|--|

| Parameter                           | Conditions                                                                 | Min.                                                                                                       | Тур. | Max.      | Units   |  |  |

| Storage Temperature Range           |                                                                            | -40                                                                                                        |      | 85        |         |  |  |

| Operating Temperature Range         |                                                                            | 0                                                                                                          |      | 55        | °C      |  |  |

| Operating Humidity                  | Noncondensing                                                              | 5                                                                                                          |      | 90        |         |  |  |

| Storage Humidity                    |                                                                            | 5                                                                                                          |      | 95        | %       |  |  |

| Altitude (without derating at 45°C) |                                                                            | 3000                                                                                                       |      |           | m       |  |  |

| Shock                               | 30G non-operating                                                          |                                                                                                            |      |           |         |  |  |

| Vibration                           | 10-500Hz, 0.5G (non-operational)                                           |                                                                                                            |      |           |         |  |  |

| MTBF                                | Per Telcordia SR-322 M1C1@40°C                                             | 559K                                                                                                       |      |           | hrs     |  |  |

| Acoustic                            |                                                                            |                                                                                                            |      | 65        | dBA/@1m |  |  |

| Safety Approvals                    | EN 60950-1:2006 +A11+A1+A2<br>BIS IS13252(Part 1):2010/ IEC 60950          | CSA 60950-1-07+A1:2011<br>ANSI/UL 60950-1-2011, Second Edition<br>IEC 60950-1:2005 (2nd Edition) + A1:2009 |      |           |         |  |  |

| Input Fuse                          | Power Supply has internal 16A/25<br>0V fast blow fuse on the AC line input | Power Supply has internal 16A/25                                                                           |      |           |         |  |  |

| Weight                              |                                                                            |                                                                                                            |      | 2.33/1.06 | lbs/Kg  |  |  |

| PROTECTI          | ON CHARACTERISTICS       |                                                                                                                                                                                                 |      |      |      |       |

|-------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Output<br>Voltage | Parameter                | Conditions                                                                                                                                                                                      | Min. | Тур. | Max. | Units |

|                   | Overtemperature (intake) | An OTP warning will be issued via the PMBus™ interface when the air inlet exceeds 65°C; however the power module shall not shut down until critical internal hotspot temperatures are exceeded. |      | 65   |      | °C    |

|                   | Overvoltage              | Latching                                                                                                                                                                                        | 13.2 |      | 14.4 | V     |

| 12V               | Overcurrent at 220Vac    | Shutdown of the output followed by auto-<br>recovery after one second. The output shall<br>attempt three such auto-recovery attempts                                                            | 140  |      | 153  |       |

|                   | Overcurrent at 120Vac    | and then enter a permanent latched state. Recovery of the permanent latched state shall require cycling of the incoming AC source or toggling of the PSON# signal.                              | 118  |      | 129  | А     |

| 12VSB             | Overvoltage              | Latching                                                                                                                                                                                        | 13.2 |      | 14.4 | V     |

| 12490             | Overcurrent              | Auto-recovery                                                                                                                                                                                   | 2.75 |      | 3    | Α     |

| ISOLATION CHARACTERISTICS               |                              |      |      |      |       |

|-----------------------------------------|------------------------------|------|------|------|-------|

| Parameter                               | Conditions                   | Min. | Тур. | Max. | Units |

| Insulation Safety Rating / Test Voltage | Input to Output - Reinforced | 3000 |      |      | Vrms  |

|                                         | Input to Chassis - Basic     | 1500 |      |      | Vrms  |

| Isolation                               | Output to Chassis            | 500  |      |      | Vdc   |

| Leakage Current                         | 1.5mA at 264Vac, 50/60Hz     |      |      |      |       |

| EMISSIONS AND IMMUNITY             |                                     |                                                                   |

|------------------------------------|-------------------------------------|-------------------------------------------------------------------|

| Characteristic                     | Standard                            | Compliance                                                        |

| Input Current Harmonics            | IEC/EN 61000-3-2                    | Complies                                                          |

| Voltage Fluctuation and Flicker    | IEC/EN 61000-3-3                    | Complies                                                          |

| Conducted Emissions                | FCC 47 CFR Part 15/CISPR 22/EN55022 | Class A, 6dB margin                                               |

| ESD Immunity                       | IEC/EN 61000-4-2                    | Level 3 criteria A                                                |

| Radiated Field Immunity            | IEC/EN 61000-4-3                    | Level 3 criteria B                                                |

| Electrical Fast Transient Immunity | IEC/EN 61000-4-4                    | Level 3 criteria A                                                |

| Surge Immunity                     | IEC/EN 61000-4-5                    | Level 3 criteria A                                                |

| Radiated Field Conducted Immunity  | IEC/EN 61000-4-6                    | Level 3 criteria A                                                |

| Magnetic Field Immunity            | IEC/EN 61000-4-8                    | 3 A/m criteria B                                                  |

|                                    |                                     | 230Vin, 100% load, Phase 0°, Dip 100% Duration 10ms (A)           |

| Voltage dips, interruptions        | IEC/EN 61000-4-11                   | 230Vin, 50% load, Phase 0°, Dip 100% Duration 20ms (VSB:A, V1:A)  |

|                                    |                                     | 230Vin, 100% load, Phase 0°, Dip 100% Duration > 20ms (VSB, V1:B) |

| STATUS AND CONTRO                        | 1/0    |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                |                     |                                                                  | Into                                                                 | rface Details                                                          |

|------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|---------------------|------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|

| Signal Name                              |        | Description The PSOK output                                                                                                                                                                                                                                                                              | in a logical "OD!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | of three intern | al aignala, ba | wayar tha autaut i  | n not atriatly a                                                 |                                                                      |                                                                        |

| PSOK (Output OK)                         | Output | "digital" signal the logic signals are 1. DC_0                                                                                                                                                                                                                                                           | · - · - · - · · - · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                |                     |                                                                  |                                                                      | n internal signal is buffered and rided with a series or pull up stor: |

|                                          |        | 3. PS_F/                                                                                                                                                                                                                                                                                                 | GOOD_H<br>\ULT_L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                |                     |                                                                  | 1.                                                                   | DC_0K_H; 1K62 series resistor                                          |

|                                          |        | The following is a upon the three in                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 | alogue levels  | of operation of the | e signal dependent                                               | 2.                                                                   | PWR_GOOD_H; 3K32 series                                                |

|                                          |        |                                                                                                                                                                                                                                                                                                          | TABLE VS. ANAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                |                     |                                                                  |                                                                      | resistor                                                               |

|                                          |        | TOOK THOTH                                                                                                                                                                                                                                                                                               | TABLE VO. AIVAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 001101          |                |                     | ODEDATION                                                        | 3.                                                                   | PS_FAULT_L; a 10K pull up                                              |

|                                          |        | DC_OK_H                                                                                                                                                                                                                                                                                                  | PWR_GOOD_H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PS_FAULT_L      | F              | SOK .               | OPERATION<br>MODE                                                | 0.                                                                   | resistor to VDD_OR (an interna<br>derived 3.3VDC rail)                 |

|                                          |        | 0                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1               | < 0.1Vdc       |                     | No AC Input                                                      |                                                                      | donvou o.ovbo runj                                                     |

|                                          |        | 0                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1               | (1/3) VDD      |                     | Invalid                                                          | The                                                                  | embedded truth table shows the                                         |

|                                          |        | 1                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1               | (2/3) VDD      | VDD = 3.3Vdc        | Standby                                                          | аррі                                                                 | ropriate levels.                                                       |

|                                          |        | 1                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1               | VDD            |                     | Power Good                                                       |                                                                      |                                                                        |

|                                          |        | X                                                                                                                                                                                                                                                                                                        | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0               | 0.2-0.4Vdc     |                     | PS Fault                                                         |                                                                      |                                                                        |

|                                          |        | The timing relation                                                                                                                                                                                                                                                                                      | onship of this sig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nal is shown in | the Timing Sp  | ecification section | that follows.                                                    |                                                                      |                                                                        |

| (FAULT/WARNING)                          |        | is intended to alert the system. This output must be driven high when the power is operating correctly (within specified limits).  The signal will revert to a high level when the warning/fault stimulus (that caused the alert) is removed.  A logic low <0.8Vdc Driven low by internal drain output). |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                |                     | gic low <0.8Vdc<br>en low by internal buffer (open<br>n output). |                                                                      |                                                                        |

| PRESENT#                                 | Output | of an (installed) p<br>Main 12Vdc outp<br>The signal is also<br>conjunction with<br>To "enable" the<br>In the host syster<br>1. If the signal<br>2. If the signal                                                                                                                                        | In the voltage level on the system side of the PSPRESENT# signal will be follows:  In the voltage level on the system side of the PSPRESENT# signal will be follows:  In the voltage level on the system side of the PSPRESENT# signal will be follows:  In the signal is also designed to control the power module during hot-plug insertion/extraction in in injunction with the host system and is provided on a short "last to make; first to break" signal pin. "enable" the Main 12Vdc output the signal requires to be pulled "high" with respect $+12V\_GND$ . If the signal is to be pulled up to the 12VSB output then the resistor value should be $21K\Omega$ When the power module is installed the voltage will be pulled the voltage will be pulled to 3.3Vdc or $12Vdc$ (host system) then the resistor value should be $5.11K\Omega$ |                 |                |                     |                                                                  |                                                                      |                                                                        |

| PS_ON<br>(Power Supply<br>Enable/Disable | Input  | "enable" the Mai<br>Alternatively, the<br>switch between '<br>The signal is pull<br>power supply ma<br>In the low state, '<br>The 12Vdc outpu                                                                                                                                                            | e PS_ON can be permanently connected to +12V_GND (via the host system mid/backplane) to nable" the Main 12Vdc output.  ernatively, the signal can be connected via the host system electronics to provide the ability to itch between "enable/disable" states.  e signal is pulled up internally via 10K to 3. A logic high >2.0Vdc  A logic low <0.8Vdc Input is via CMOS Schmitt trigger buffer.  wer supply main 12Vdc output will be enabled when this signal is pulled low to +12V_GND. the low state, the signal input shall source a nominal 1.2mAdc.  e 12Vdc output will be disabled when the input is driven higher than 2.4V, or open circuit. Cycling is signal shall clear latched fault conditions.                                                                                                                                     |                 |                |                     |                                                                  | gic high >2.0Vdc<br>gic low <0.8Vdc<br>t is via CMOS Schmitt trigger |                                                                        |

| ADDR (Address Select)                    | Input  | microprocessor)<br>Connection of a s                                                                                                                                                                                                                                                                     | analogue input that is used to set the address of the internal slave devices (EEPROM and croprocessor) used for digital communications.  nnection of a suitable resistor to +12V_GND, in conjunction with an internal resistor divider chain, I configure the required address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                |                     |                                                                  | •                                                                    |                                                                        |

| STATUS AND CONTR   | STATUS AND CONTROL SIGNALS (CONTINUED) |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |  |  |  |  |  |

|--------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| Signal Name        | 1/0                                    | Description                                                                                                                                                                                                                                                                                                                                                             | Interface Details                                                                     |  |  |  |  |  |

| SCL (Serial Clock) | Both                                   | A serial clock line compatible with PMBus <sup>™</sup> Power Systems Management Protocol Part 1 – General Requirements Rev 1.1.  No additional internal capacitance is added that would affect the speed of the bus.  The signal is provided with a series isolator device to disconnect the internal power supply bus in the event that the power module is unpowered, | VIL is 0.8V maximum<br>VoL is 0.4V maximum when sinking<br>3mA<br>VIH is 2.1V minimum |  |  |  |  |  |

| SDA (Serial Data)  | Both                                   | A serial data line compatible with PMBus <sup>™</sup> Power Systems Management Protocol Part 1 – General Requirements Rev 1.1.  The signal is provided with a series isolator device to disconnect the internal power supply bus in the event that the power module is unpowered,                                                                                       | VIL is 0.8V maximum<br>VoL is 0.4V maximum when sinking<br>3mA<br>VIH is 2.1V minimum |  |  |  |  |  |

| IMONITOR           |                                        | An analogue DC output voltage signal directly proportional to load current and can be used as an indication of the power supply's load current. This signal of multiple connected units should not be tied together.                                                                                                                                                    | Analogue output voltage:<br>60.15mV/Amp                                               |  |  |  |  |  |

| ST | STATUS INDICATOR CONDITIONS |             |                                                                                                        |  |  |  |  |  |

|----|-----------------------------|-------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|    | LED State                   | Mode        | Operating Condition                                                                                    |  |  |  |  |  |

| 1. | Off                         | AC Turn-off | The incoming AC source is below the minimum power module turn-on specification                         |  |  |  |  |  |

| 2. | Green – blinking 1Hz        | Standby     | The power module VStandby output is operating within normal parameters and main output is disabled     |  |  |  |  |  |

| 3. | Green – solid               | Power-good  | The power module active; VStandby & Main outputs are operating within normal parameters and delivering |  |  |  |  |  |

| 4. | Yellow – blinking 1Hz       | Warning     | A warning condition within the power supply has been detected                                          |  |  |  |  |  |

| 5. | Yellow – solid              | Fault       | A fault condition within the power supply has been detected.                                           |  |  |  |  |  |

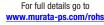

| TIMING SPECIFICATIONS |                                                                           |     |      |      |  |  |

|-----------------------|---------------------------------------------------------------------------|-----|------|------|--|--|

| Parameter             | Description                                                               | Min | Max  | Unit |  |  |

| Tsb_0n                | Delay from AC being applied to standby output being within regulation     | 0   | 3000 | ms   |  |  |

| Tsb_Vout              | Delay from standby output to main output voltage being within regulation  | 50  | 500  | ms   |  |  |

| TPWR_G00D_0n          | Delay from output voltages within regulation limits to PWR_GOOD assertion | 20  | 500  | ms   |  |  |

| TAC_OK_OFF            | Delay from loss of AC to deassertion of AC_OK                             | 20  | 60   | ms   |  |  |

| TAC_OK_On             | Delay from AC being applied to assertion of AC_OK                         | 1   | 3000 | ms   |  |  |

| TPWR_G00D_Hold-up     | Delay from loss of AC to deassertion of PWR_GOOD                          | 7   | 30   | ms   |  |  |

| TVout_Hold-up         | Delay from loss of AC to main output being out of regulation              | 12  | 20   | ms   |  |  |

| Tsb_Hold-up           | Delay from loss of AC to standby output being out of regulation           | 20  | 2000 | ms   |  |  |

| TPWR_G00D_0FF         | Delay from deassertion of PWR_GOOD to output falling out of regulation    | 0   | 2    | ms   |  |  |

| TPSON_On_Delay        | Delay from PSON assertion to output being within regulation               | 1   | 200  | ms   |  |  |

| Pin# Fu             | unction     | Pin Type         | Description                                                                                                     |                               |                |

|---------------------|-------------|------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|----------------|

| 14-26, 39- +1<br>51 | 12V_GND/RTN | Power<br>Ground  | Power and Standby Return                                                                                        |                               |                |

| 1-13, 52-64 +1      | 12V         | Power            | 12V Output                                                                                                      |                               |                |

| 37 +1               | 12VSB       | Power            | 12V Standby Output                                                                                              | Power Supply Output Card Edge |                |

| 38 PS               | SINTERRUPT  | Output           | Active low; interrupt line for power supply fault & warning detection as per PMBus <sup>TM</sup> spec           | 75 64 1                       |                |

| 36 PF               | RESENT#     | Input            | Power Supply Present Signal (shortest pin)                                                                      | // 📕                          | \ \            |

| 35 PS               | SOK         | Analog<br>output | Combination of three power supply output indicator signals:  1. AC input 0K 2. Power Good 3. Power Supply Fault |                               |                |

| 34 <u>IM</u>        | MONITOR     | Analog I/O       | main output current signal ypical analog voltage shall be 60.15mV/Amp of main output current.                   |                               |                |

| 33 PS               | SON#        | Input            | Power Supply on/off control signal                                                                              |                               |                |

| 32 SC               | CL          | Input            | SMBus/PMBus Clock                                                                                               | PCB Top Side                  | PCB Bottom Sig |

| 31 SE               | DA          | I/O              | SMBus/PMBus Data                                                                                                |                               |                |

| 30 +1               | 12V_GND/RTN | Analog I/O       | Power Supply Signal Ground                                                                                      |                               |                |

| 29 N/.              | /A          | N/A              | Reserved; no User connection                                                                                    |                               |                |

| 28 N/.              | /A          | N/A              | Reserved; no User connection                                                                                    |                               |                |

| 27 AD               | DDR         | Analog input     | PMBus Address                                                                                                   |                               |                |

86mm 1U Front End AC-DC Power Supply

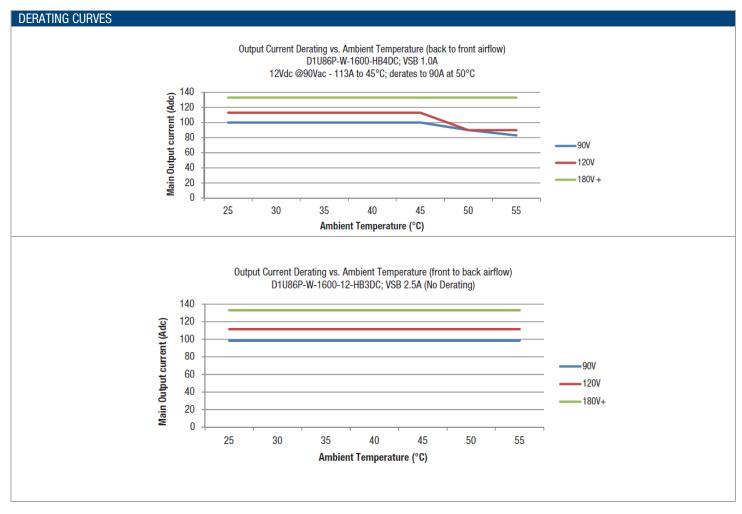

#### **CURRENT SHARING NOTES**

Main Output: Current share is achieved using the droop method. Nominal output voltage (12.20V) is achieved at 50% load and output voltage varies at a rate of 3.10mv per amp increase/decrease. Startup of parallel power supplies is not internally synchronized. If more than 1600W combined power is needed, start-up synchronization must be provided by using a common PS\_ON signal. To account for ±5% full load current sharing accuracy and the reduction in full load output voltage due to droop, available output power must be derated by 10% when units are operated in parallel.

The Standby output can be tied together for redundancy however the total combined power must not exceed the Standby rail capability (30W) of a single supply. Internal MOSFET ORING devices are employed.

86mm 1U Front End AC-DC Power Supply

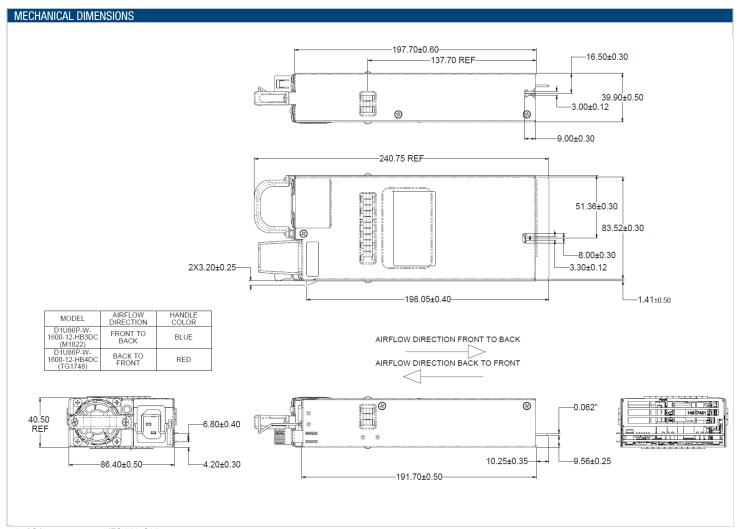

- 1. AC input connector: IEC 320-C14

- 2. 86.4mm x 197.7mm x 40.5mm [3.4" x 7.78" x 1.59"]

- This drawing is a graphical representation of the product and may not show all fine details.

Reference File: D1U86P-W-1600-12-HBxDC (TG1748-M1822)\_Drawing for Product Datasheet\_20160106.PDF

| MATING CONNECTOR   |             |  |  |

|--------------------|-------------|--|--|

| Part Number        | Description |  |  |

| FCI 10053363-200LF | Right Angle |  |  |

| FCI 10046971-001LF | Vertical    |  |  |

| OPTIONAL ACCESSORIES             |                |  |  |  |

|----------------------------------|----------------|--|--|--|

| Description                      | Part Number    |  |  |  |

| 12V D1U86P Output Connector Card | D1U86P-12-CONC |  |  |  |

| APPLICATION NOTES |                                         |                                                              |  |  |  |

|-------------------|-----------------------------------------|--------------------------------------------------------------|--|--|--|

| Document Number   | Description                             | Link                                                         |  |  |  |

| ACAN-50           | D1U86P-12-CONC Interface Connector Card | https://power.murata.com/datasheet?/data/apnotes/acan-50.pdf |  |  |  |

| ACAN-51           | D1U86P PMBus™ Communication Protocol    | https://power.murata.com/datasheet?/data/apnotes/acan-51.pdf |  |  |  |

Murata Power Solutions, Inc. 129 Flanders Rd. Westborough, Ma 01581, USA. ISO 9001 REGISTERED

This product is subject to the following operating requirements and the Life and Safety Critical Application Sales Policy. Refer to: https://www.murata-ps.com/requirements/

Murtal Power Solutions, Inc. ("Nurtal") makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of itenses to make, use, or sell equipment constructed in accordance therewith. Buyer represents and agrees that it has all the necessary expertise to rectae and implement safeguards that anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm, and take apomprishe remedial actions. Buyer will fully indemnify Murtal, its affiliated companies, and its presentatives against any damages arising out of the use of any Murtal products in safety-critical applications. Specifications are subject to change without notice.